How do you shift right in Verilog?

Sarah Duran

Updated on March 06, 2026

How do you shift right in Verilog?

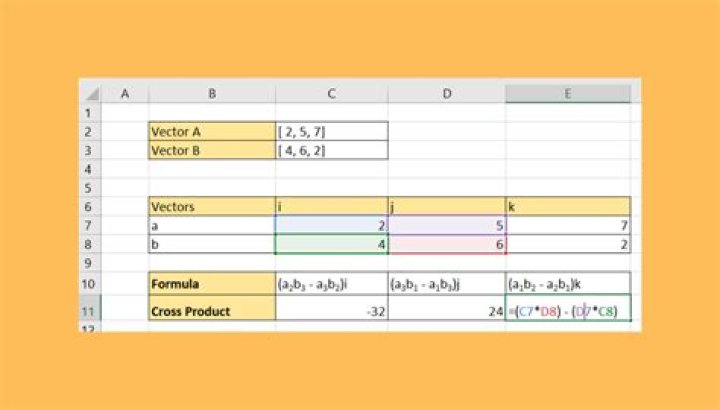

The shift operator in Verilog is used to shift data in a variable….Create shift registers, shift left, shift right in your FPGA or ASIC.

| Shift Operators in Verilog | |

|---|---|

| >> | Shift Right, Logical (fill with zero) |

| <<< | Shift Left, Arithmetic (keep sign) |

| >>> | Shift Right, Arithmetic (keep sign) |

What is << in Verilog?

<< is a binary shift, shifting 1 to the left 8 places. 4’b0001 << 1 => 4’b0010. >> is a binary right shift adding 0’s to the MSB. >>> is a signed shift which maintains the value of the MSB if the left input is signed.

What is the difference between >> and >>> in Verilog?

According to IEEE1800-2012 >> is a binary logical shift, while >>> is a binary arithmetic shift.

How do you write XOR in Verilog?

Groups of Verilog operators are shown on the left….Operators.

| Verilog Operator | Name | Functional Group |

|---|---|---|

| == != | logical equality logical inequality | equality equality |

| === !== | case equality case inequality | equality equality |

| & | bit-wise AND | bit-wise |

| ^ ^~ or ~^ | bit-wise XOR bit-wise XNOR | bit-wise bit-wise |

What is logical shift right?

In computer science, a logical shift is a bitwise operation that shifts all the bits of its operand. Shifting right by n bits on an unsigned binary number has the effect of dividing it by 2n (rounding towards 0). Logical right shift differs from arithmetic right shift.

How do you find the arithmetic right shift?

A right arithmetic shift of a binary number by 1. The empty position in the most significant bit is filled with a copy of the original MSB. A left arithmetic shift of a binary number by 1. The empty position in the least significant bit is filled with a zero….Arithmetic shift.

| Language or processor | Left | Right |

|---|---|---|

| Z80 | SLA | SRA |

When would you use a Casex vs a casez statement?

From the spec: “The casez and casex keywords can be used instead of case, with the same semantics. In other words, during pattern matching, wherever 2 bits are compared (whether they are tag bits or members), the casez form ignores z bits, and the casex form ignores both z and x bits.”

What is SystemVerilog used for?

SystemVerilog, standardized as IEEE 1800, is a hardware description and hardware verification language used to model, design, simulate, test and implement electronic systems.

What is the difference between == and === in SV?

== can be synthesized into a hardware (x-nor gate), but === can’t be synthesized as x is not a valid logic level in digital, it is infact having voltages in between 0 and 1. And z is not itself any logic, it shows disconnection of the circuit.

What is the difference between wire and reg?

wire elements must be continuously driven by something, and cannot store a value. Henceforth, they are assigned values using continuous assignment statements. reg can be used to create registers in procedural blocks. Thus, it can store some value.

Which of the following loops are supported by Verilog?

In Verilog, there are four different types of looping statements.

- Forever loop. This loop will continuously execute the statements within the block.

- Repeat loop. This will execute statements a fixed number of times.

- ile loop.

- For loop.

Which loop statement is not used in Verilog HD?

If expression evaluates to high impedance or un-known, then statement will not be executed. while Loop: while loop repeats the statement until the expression returns true. If starts with false value, high impedance or unknown value, statement will not be executed.